シミュレーションの部 審査方法

シミュレーションの部には, 以下に示す5部門があります. トポロジー部門を除く各部門では, それぞれの評価式に従い得点を算出し,順位を定めます. 各審査項目名をクリックすると, 審査項目の評価方法が表示されます.

1.スルーレート・消費電流・同相入力範囲・直流利得 部門

審査項目:スルーレート 消費電流 同相入力範囲 直流利得

評価式:(スルーレート × 同相入力範囲 × 直流利得)/消費電流

2.消費電力・出力抵抗・入力換算雑音・利得帯域幅積・位相余裕 部門

審査項目:消費電力 出力抵抗 入力換算雑音 利得帯域幅積 位相余裕

評価式:(利得帯域幅積 × 位相余裕 )/(消費電力^2 × 出力抵抗 × 入力換算雑音)

3.位相余裕・占有面積・消費電流・同相除去比・電源電圧 部門

審査項目:位相余裕 占有面積 消費電流 同相除去比 電源電圧

評価式:(位相余裕 × 同相除去比)/(占有面積 × 消費電流 × 電源電圧)

4.電源電圧変動除去比・出力電圧範囲・位相余裕 部門

審査項目:電源電圧変動除去比 出力電圧範囲 位相余裕

評価式:電源電圧変動除去比 × 出力電圧範囲 × 位相余裕

5.トポロジー 部門

審査項目:トポロジー, 緒特性のシミュレーション結果, 設計者のコメント

(※但し、評価式では直流利得、同相除去比、電源電圧除去比はデシベルではなくリニア値で評価

する)

-

- 電源電圧

- 審査する値

- 応募者が申告した電源電圧

電源電圧は単電源の場合その電源電圧を, 両電源の場合正負の電源の絶対値の和を意味します. 以下の各項目の審査においてもこの電源電圧を用います.

単電源で応募された場合も評価には両電源(指定された電源電圧の半分の電圧を持った正負の電源を用い, 正負の電源の中間を接地(0電位)とします.- 申告された電源電圧を仕様時に演算増幅器が要件を満たさない場合や5V以上の電源電圧が指定された場合は, 審査の対象外となるので注意してください.

- 応募者が申告した電源電圧

-

- 消費電流

- 回路構成

- Fig. 1 参照

- Fig. 1 参照

- 解析の種類

- 直流解析

- 直流解析

- 審査する値

- 非反転入力端子接地時(Fig.1中の Vin=0としたとき)に電源(VDD)から流れ出る全電流

-

- 消費電力

- 回路構成

- Fig. 1 参照

- Fig. 1 参照

- 解析の種類

- 直流解析

- 直流解析

- 審査する値

- (設計者が指定した電源電圧)×(電源から流れ出る全電流).

- (設計者が指定した電源電圧)×(電源から流れ出る全電流).

-

- 出力抵抗

- 回路構成

- Fig. 1 参照

- Fig. 1 参照

- 解析の種類

- 直流小信号伝達関数解析

- ネットリストの書式: .tf V(出力ノード名) 入力信号源名

- 審査する値

(上記の書式で得られたFig. 1 の出力抵抗) ×(審査項目5で求める直流利得+1) - 直流小信号伝達関数解析

-

- 直流利得

- 回路構成

- Fig. 2参照

- Fig. 2参照

- 解析の種類

- 交流解析

- ネットリストの書式: .AC DEC 100 1 10g

- 審査する値

- 入力信号の周波数が1Hzのときの利得

- 交流解析

-

- 利得帯域幅積

- 回路構成

- Fig. 1参照

- Fig. 1参照

- 解析の種類

- 交流解析

- ネットリストの書式: .AC DEC 100 1 10g

- 審査する値

- Fig. 1に示す回路の利得が周波数1Hz時の利得より−3dBとなる周波数

- 交流解析

- 位相余裕

- 回路構成

- Fig. 2参照

- Fig. 2参照

- 解析の種類

- 交流解析

- ネットリストの書式: .AC DEC 100 1 10g

- 審査する値

- (180度)−(直流から振幅特性が 0dB となる周波数までの最大の位相遅れ)

または

(直流から振幅特性が 0dB となる周波数までの最大の位相進み)- (180度)

の値の小さい方 - 交流解析

- 入力換算雑音

- 回路構成

- Fig. 3参照,

- (但し帰還抵抗(100M)には雑音を生じない理想素子を用います.)

- Fig. 3参照,

- 解析の種類

- 雑音解析

- ネットリストの書式(出力端子outに現れる雑音を入力端子VINに換算する場合):

- .AC DEC 100 1 1meg

- .NOISE V(out) VIN

- 審査する値

- 1Hzから1MHまでのノイズの総和

- 雑音解析

- スルーレート

- 回路構成

- Fig. 4参照

- Fig. 4参照

- 解析の種類

- 過渡解析

- 入力パルスの書式:

立ち上がりの場合

- VIN inp 0 DC 0 PULSE 0 2.5 100n 1n 1n 6u 7u

立ち下がりの場合

VIN inp 0 DC 0 PULSE 0 -2.5 100n 1n 1n 6u 7u

- 審査する値

- Fig. 4の回路を用い立ち上がり時と立ち下がり時のスルーレートを評価します.

- 但し, スルーレートを

出力電圧Voutが収束してからの電圧をVsetとした時に

スルーレート=dVout/dt@(Vout=Vset/2)と定義します.

立ち上がり時と立ち下がり時のスルーレートを評価し、審査にはそれらの絶対値の小さい方を用います.

スルーレートの評価に用いるステップ入力は上記書式で指定される波形を用います.- 立ち上がりでは0Vから2.5Vに変化するステップ入力で、立ち下がりでは0Vから-2.5Vに変化するステップ入力を用います.

- 過渡解析

- 同相除去比(CMRR)

- 回路構成

- Fig. 5参照

- Fig. 5参照

- 解析の種類

- 交流解析

- 交流解析

- 審査する値

- Fig. 5中左の回路(Fig. 2と同等)より差動利得(Ad)を, 右の回路より同相利得(Ac)をそれぞれ求めます. それらを用いてCMRR(=Ad/Ac)の周波数特性を1 Hz〜10 GHzまで求めその最大値を審査します.

- Fig. 5中左の回路(Fig. 2と同等)より差動利得(Ad)を, 右の回路より同相利得(Ac)をそれぞれ求めます. それらを用いてCMRR(=Ad/Ac)の周波数特性を1 Hz〜10 GHzまで求めその最大値を審査します.

- 同相入力電圧範囲

- 回路構成

- Fig. 6参照

- Fig. 6参照

- 解析の種類

- 直流解析

- 直流解析

- 審査する値

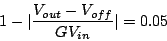

まず入力電圧 Vinを0から増加させ,上式が初めて成り立つVin(ここでは説明のためVin+とします)を求めます.次にVinを0から減少させた時についても同様に,上式が初めてなりたつときのVin(Vin-とする)をもとめます.

同相除去比・直流利得・同相入力範囲部門の評価には

0.55*(Vin+-Vin-) [V]

を用います. 但し,VoffおよびGはそれぞれVinを0としたときの出力電圧 Voutと図6の回路の利得(0.25)とします.

- 出力電圧範囲

- 回路構成

- Fig. 7参照

- Fig. 7参照

- 解析の種類

- 直流解析

- 直流解析

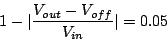

- 審査する値

まず入力電圧 Vinを0から増加させ,上式が初めて成り立つVin(ここでは説明のためVin+とします)を求めます.次にVinを0から減少させた時についても同様に,上式が初めてなりたつときのVin(Vin-とします)をもとめます.

- 評価には100×{Vin+-Vin-}/VDDを用います. 但し,VoffはVinを0としたときの出力電圧Voutとします.

- 電源電圧変動除去比(PSRR)

- 回路構成

- Fig. 8参照

- Fig. 8参照

- 解析の種類

- 交流解析

- 交流解析

- 審査する値

- PSRR=Ad÷(一方の電源端子から入力を加えたときの出力端子での利得)

の周波数特性を求め、1Hzにおける値を審査する. 正負の電源それぞれについて行い, その値の小さい方を審査に用います. - PSRR=Ad÷(一方の電源端子から入力を加えたときの出力端子での利得)

- 回路占有面積

- 使用した全MOSFETのチャネル面積(チャネル幅×チャネル長), ソース領域(チャネル幅×0.6u), ドレイン領域((チャネル幅×0.6u))および抵抗, 容量に必要となる面積の総和を評価します. 但し, 全ての抵抗は最小線幅0.4umを使用すると仮定します.

- トポロジー

- 回路構成上の工夫, アイディア等を評価します.

トポロジーの評価の際には「回路図」と共に提出データの「回路の特長に関する説明文」を参照し評価を行いますので, 説明文には回路の設計時に工夫した点を記載してください.